### Improved hybrid SET/MOS Digital-Analog and Analog-Digital Converters

### المحولات الرقمية التناظرية و التناظرية الرقمية المحسنة باستخدام الدوائر. المختلطة (SET/MOS )

Eng. Lobna A. Osman, Prof. Sameh E. Rehan, and Prof. Abdel-Fattah I. Abdel-Fattah Communications and Electronics Engineering Department, Faculty of Engineering, Mansoura University (MU), Mansoura, EGYPT 35516 Corresponding author: E-mail: englobna20@yahoo.com Tel.: +20 1094704854

#### ملخص البحث

دوائر تحويل الإشارات الرقمية والتناظرية هي دوائر مهمة، لأنها يمكن أن تستخدم في أنظمة معالجة الإشارات، وأنظمة معالجة الصورة وأنظمة الاتصالات. معظم الباحثين في الوقت الحاضر مهتمين بكيفية الحد من تبديد الطاقة وبناء الدوائر المدمجة، وزيادة سرعة التحويل .هذا البحث يقدم نوعين من المحولات الرقمية التناظرية و التناظرية الرقمية المحسنة باستحدام الدوائر المختلطة SET/MOS.

دوائر المحولات الرقمية التناظرية و التناظرية الرقمية المختلطة SET/MOS لديها مزايا دائرة SET و دائرة MOS. تم استخدام نموذج PSPICE العلاقة التكرارية (RRM) مع أربع حالات للشحنة للتر انزستور أحادى الالكترون. تم محاكاة دوائر المحولات الرقمية التناظرية النانوية المختلطة SET/MOS المحسنة (على ن = 4 و 8) باستخدام جهاز المحاكاة SET/MOS المحولات الرقمية التناظرية النانوية المختلطة SET/MOS المحسنة (على ن = 4 و 8) باستخدام جهاز المحاكاة حوائر المحولات الرقمية التناظرية النانوية المختلطة SET/MOS المحسنة (على ن = 4 و 8) باستخدام جهاز المحاكاة SET/MOS المحولات الرقمية التناظرية النانوية المحتلطة SET/MOS المحسنة (على ن = 4 و 8) باستخدام جهاز المحاكاة والزر المحولات الرقمية التناظرية و التناظرية الرقمية المختلطة SET/MOS (على ن = 8 و 8). اظهرت النتائج ان دوائر المحولات الرقمية التناظرية و التناظرية الرقمية المحسنة المقترحة لها مميزات وهى قدرة القيادة العالية وتحسين اشارة الخرج التى هى احسن من دوائر المحولات التى تستخدم الترانزستور احادى الالكترون فقط دوائر المحولات الرقمية التناظرية لديها شكل الدوائر المحمولات التى تستخدم الترانزستور احادى الالكترون فقط دوائر المحولات الرقمية التناظرية لديها شكل الدوائر المحمجة وارتفاع كثافة التكامل والسر عة العالية وارتفاع قيادة الحمل وفقد اقل القدرة مقارنة مع دوائر مختلطة تستخدم SET/MOS

### Abstract

Digital and analog signal conversion circuits are important circuits as it can be used in signal processing systems, image processing and communication systems. The most researchers nowadays are interested with how to reduce power dissipation, compact circuit structure, and increase the speed of conversion. This paper present two types of improved hybrid SET/MOS DAC and ADC circuits. The SET/MOS hybrid ADC and DAC circuits have the advantages of the SET circuit and the MOS circuit. The PSPICE Recursion Relation Model (RRM) with four charge states of the SET transistor was used. The improved hybrid n-bit DAC nano-circuits are simulated (for n = 4 and 8) using Orcad Capture PSPICE simulator. The performance of the SET/MOS hybrid n-bit ADC circuits have the advantages of high driving capability and the enhanced swing of the output signal which is better than pure SET ADC and DAC circuits. The improved n-bit DAC nano-circuit structure, higher integration density, high speed, high load drivability, and low-power dissipation compared with the previously reported SET/MOS hybrid DAC.

### Keyword

Single Electron Transistor (SET), MOS transistor, Nano-circuits, hybrid, Analog-Digital Converter (ADC), Digital-Analog Converter (DAC), Recursion Relation Model (RRM), room-temperature, PSPICE.

#### 1. Introduction

Feature size reduction in microelectronic circuits has been an important factor to the dramatic increase in the processing power of computer arithmetic circuits. However, it is generally accepted that sooner or later MOS based circuits cannot be reduced further in feature size due to fundamental physical restrictions [1]. The rapid progress in the fabrication technology of silicon nano devices has pushed the device dimension toward nanometer scale. When device dimensions are reduced to a few nanometer range, the single electron tunneling leads to interesting new device characteristics. If we wished to continue obeying the Moore law and make the circuits cheaper, faster and the power dissipation lower. some new electronic devices would have to be created, such as Single-Electron Transistor (SET)[2]. Single Electron Transistor (SET) is expected to be the future of VLSI design due to its nanoscale feature-size, ultra low power dissipation and high density. Compared with other nano-devices, SET is a new device because of its advantages of little size, low operating power, high integration and easy to combine with MOS[3]. The fundamental principle of single-electronic is the Coulomb blockade, which was first observed and studied by Gorter [4]. Pure SET circuits have very limited applications due to SET's low current drivability, small voltage gain and low-temperature operation, since MOS advantages devices have that can compensate for the disadvantages of SET, SET/MOS architecture hybrid which combines the advantages of both MOS and SET. Tunnel junction is the basic unit cell in Single Electron Transistor. It consists of two pieces of metal separated by a very thin (~1nm) insulator [2]. The basic singleelectron nano-devices is the tunnel junction which can be thought of as a leaky capacitor, through which the movement of individual

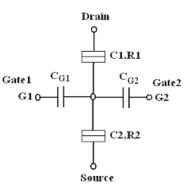

electrons can be controlled [23]. Fig. 1

shows the symbol of a SET device. It consists of two tunnel junctions in series sharing a common electrode, which is called the island, also known as the quantum dot and two gates are coupled to the island. Any single-electron (SE) circuit has at least one floating node, between connected tunnel junctions and/or capacitors, that is called an island or a quantum dot (QD) [24].

The orthodox theory is the description of charge transport utilizing free energy, tunnel rates, coulomb blockade and quantization of charge transport [25].

Fig. 1. Single Electron Transistor symbol

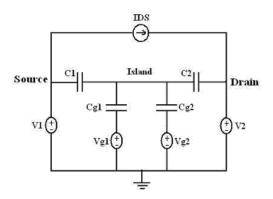

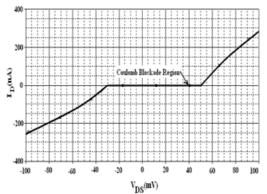

Lientschnig et al. 2003 [5] introduced an exact model for Single-Electron Transistor and named it Recursion Relation Model (RRM). This model uses the orthodox theory of singleelectron tunneling determines the and occupation probabilities of states. The RRM model is shown in Fig. 2, which consists of two tunnel junctions, two gates are coupled to the island, a voltage source is connected to the source, the drain, and the two gates. This model uses eleven charge states. In this paper, RRM model with four-charge states were used in the simulation to reduce the time, current and the power dissipation using OrCAD PSPICE. The current-voltage Capture characteristics  $(I_D - V_{DS})$  of the SET at V<sub>GS</sub>=0.02V are shown in Fig. 3 using fourstates RRM model by OrCAD Capture PSPICE.

Fig. 2. Single Electron Transistor model in PSPICE

Fig. 3. The current-voltage characteristics ( $I_{D}\text{-}V_{DS})$  of the SET

Digital and analog signal conversion circuits are useful circuits, it can be used in signal processing systems, image processing and communication systems. The Analog-to-Digital Conversion (ADC) and Digital-to-Analog conversion (DAC) are developed to obtain high integration density, high speed, and low power dissipation. The advantages of ADC and DAC circuits which uses Single Transistor are Electron low power dissipation, high integration density and high speed. Some research groups had proposed several kinds of ADC and DAC circuits based on SET [6]–[11]. An improved hybrid SET/MOS DAC and ADC circuits were presented in this paper to take the advantages of the proposed SET/MOS architecture for high temperature operation and driving capability. Their advantages are low power dissipation, small size, circuits have large load capability and large signal swing. In this paper, DAC using hybrid SET/MOS circuit is illustrated in section 2. ADC using hybrid SET/MOS circuit is introduced in section 3. ADC circuit using SET is simulated in section 4. Finally, conclusions are given in section 5 followed by the references.

## 2. DAC using hybrid SET/MOS circuit

## 2.1. Operating principle for n-bit hybrid SET/MOS DAC circuit

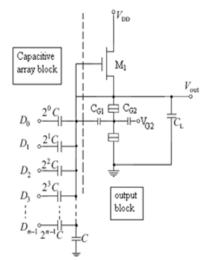

Fig. 4 shows the basic schematic of an n-bit hybrid SET/MOS DAC circuit. It consist of two parts, the first part is a signal input capacitive array block, the second part is a Single Electron Transistor in series with depletion type NMOS (output block). The ratio of capacitor's values is  $2^0:2^1:2^2:2^3:\ldots:2^n$  in the capacitance array.

When an n-bit digital signal  $D_0, D_1, D_2, \dots, D_{n-1}$ applied is to the capacitance array (first part), the output of the capacitance array is connected with the input of the output circuit (second part) which consists of SET in series with NMOS. The NMOS transistor M<sub>1</sub> acts as the load of SET, its gate is connected with the source. In this circuit Single Electron Transistor was used with two gates, the first gate  $(G_1)$  acts as signal input end; the second gate  $(G_2)$  is used to control the phase of SET. The second gate of SET  $(G_2)$  also has the function to compensate the background charge. This circuit structure was proposed by authors in [12], [13].

The input gate of the SET and the source of NMOS are shorted in the output circuit (second part). The drain current of the SET oscillates periodically with the increase of input voltage signal at the input gate [14]. The analog voltage is used as output signal of the hybrid DAC circuit.

Fig. 4. Schematic of n-bit hybrid SET/MOS DAC circuit

### 2.2. Simulation results of 4-bit and 8-bit DAC circuits

This circuit is SET/MOS hybrid DAC circuit, which is difficult to simulate using the MOS circuit simulation method or the SET circuit simulation method separately. Therefore the Recursion Relation Model (RRM) with four charge states using OrCAD Capture PSPICE program that is used in the circuit by the double-gate SET simulation model. The parameters of resistances and capacitances are set as follows:

The tunnel junction resistance  $(R_1,R_2)$  to be greater than the quantum resistance (~26 k $\Omega$ ) to confine the electrons in the island; the charging energy of the island capacitance to be larger than the available thermal energy to avoid electron tunneling due to the thermionic emission, namely,  $e^2/2C_{\Sigma}>k_BT$ [14]. Where  $C_{\Sigma}=C_1+C_2+C_{G1}+C_{G2}$  is the total capacitance of the island with respect to the ground,  $k_B$  is the Boltzmann's constant, and T is absolute temperature [15].

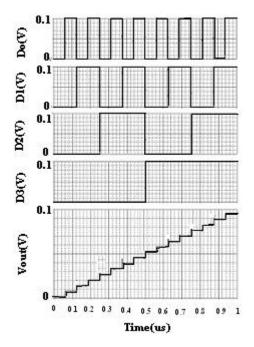

Compared with pure SET DAC circuit [16],[17], the proposed hybrid SET/MOS DAC uses fewer electronic components, which simplifies the structure of the circuit, increase the operating temperature, enhances the load capability and the signal output scope. Fig. 5 shows the simulation results

waveform of 4-bit DAC circuit using Orcad Capture PSPICE. Fig. 6 shows the simulation results waveform of 8-bit DAC circuit using Orcad Capture PSPICE.

Fig. 5. PSPICE simulation results for the proposed 4-bit hybrid DAC

Compared with DAC circuit in [14]. The improved hybrid SET/MOS DAC uses fewer electronic components, simplifies the structure of the circuit, enhances the load capability and the signal output. The power dissipation of designed 4-bit DAC is 3.25E-11W, which is lower than the previous proposed SET/MOS DAC [14]. Table 1 shows a comparison between the previously reported DAC in [14] and the improved DAC.

Fig. 6. PSPICE simulation results for the proposed 8-bit hybrid DAC

| The simulation parameters      | Hybrid 4-bit<br>DAC [14]                                                                                                           | Improved DAC                                                                                                                  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Power supply voltage           | 0.3V                                                                                                                               | 0.1V                                                                                                                          |  |

| Power<br>dissipation           | 2.52E-10W                                                                                                                          | 3.25E-11W                                                                                                                     |  |

| Capacitance<br>Array Block (F) | C=1E-12F                                                                                                                           | C=10E-12F                                                                                                                     |  |

| Capacitive drive capability    | several fFs                                                                                                                        | several hundreds<br>of fFs=500fF                                                                                              |  |

| Temperature<br>(K)             | 100K                                                                                                                               | 20-1000K                                                                                                                      |  |

| Total job time                 | 38.27Sec                                                                                                                           | 15.86Sec                                                                                                                      |  |

| SET<br>parameters              | $\begin{array}{c} C_{G1}{=}1.8E{-}18F\\ C_{G2}{=}0.64E{-}18F\\ C_{1}{=}\ C_{2}{=}1E{-}19F\\ R_{1}{=}R_{2}{=}2E6\Omega \end{array}$ | $\begin{array}{c} C_{G1}{=}2E{-}18F\\ C_{G2}{=}0.7E{-}18F\\ C_{1}{=}C_{2}{=}1E{-}19F\\ R_{1}{=}R_{2}{=}1E6\Omega \end{array}$ |  |

| NMOS<br>parameters             | M <sub>1</sub> : L= 150nm<br>W= 30nm<br>Depletion type                                                                             | $\begin{array}{l} M_1: L=150nm \\ W=15nm \\ V_{to}=-0.018V \\ Depletion type \end{array}$                                     |  |

Table 1. Comparison between the previously reported DAC in [14] and the improved DAC

# **3. ADC using hybrid SET/MOS circuit**

## 3.1. Operating principle for n-bit hybrid SET/MOS ADC circuit

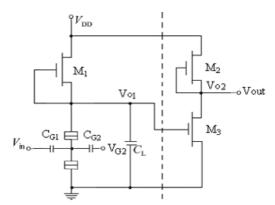

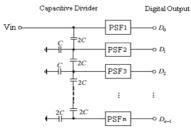

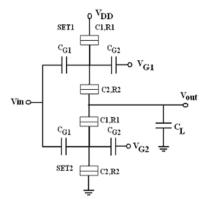

Fig. 8 shows the schematic of an n-bit hybrid SET/MOS ADC circuit, which consists of a capacitive divider and n Periodic Symmetric Function (PSF) with the same circuit parameters[18]. The PSF circuit is composed of two cascade circuits that are shown in Fig. 7. The first part is a SET in series with depletion type NMOS (the same as the output circuit of DAC), the second part is a common source amplifier circuit. The ADC operation as follow:

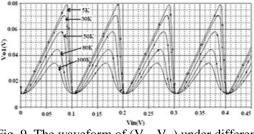

The analog input signal  $V_{in}$  is divided by the signal divider into n voltage signals ( $V_{in}/2^i$ , i= 0,1,2,...,n-1). Then, the analog signals are converted into the corresponding binary output signal by the PSF units with the same circuit parameters[14]. Fig. 9 shows the ( $V_{o1}-V_{in}$ ) waveform of PSF at different temperatures (5, 30, 50, 80, 100K). From the figure as the temperature increase, the output of the first part  $V_{o1}$  become smoother.

Fig. 7. Schematic of a complementary SET/MOS Periodic Symmetric Function (PSF)

Fig. 8. Architecture for an n-bit ADC

Fig. 9. The waveform of  $(V_{o1}-V_{in})$  under different temperature

### 3.2. Simulation results of 3-bit and 8-bit ADC circuits

The operating temperature of hybrid SET/MOS device should be chosen carefully, this will adequately embody the performance of SET device and MOS device [14]. Compared with previous proposed SET/MOS ADC [19], the proposed 3-bit ADC circuit has only one power supply and it can operate at higher temperature. Compared with the previous proposed SETbased ADC [8], [11], [20], the proposed

hybrid SET/MOS ADC is enhanced in operation temperature from 0K~10K to 144K, heightened the load capability and signal output scope.

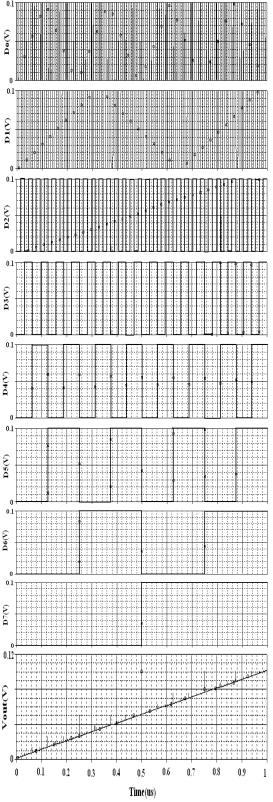

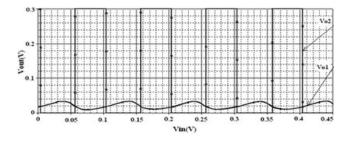

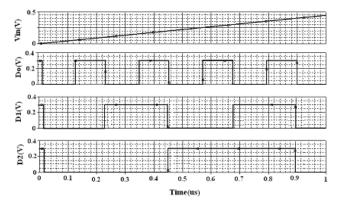

Fig. 10 shows Voltage Transfer the Characteristics of SET/MOS Periodic Symmetric Function (PSF) at 100K. Fig. 11 show the simulation results of 3-bit ADC circuit using Orcad Capture PSPICE, the first waveform is the input ramp voltage, the rest of the waveform show the digital output signal  $D_0$ ,  $D_1$  and  $D_2$ . An 8-bit ADC circuit was simulated using Orcad Capture PSPICE. Fig. 12 show the simulation results of 8-bit ADC circuit. Table 2 shows a comparison between the previously reported ADC in [14] and the improved ADC.

Fig. 10. Voltage Transfer Characteristics of Periodic Symmetric Function (PSF)

Fig. 11. Simulated waveform of 3-bit ADC Hybrid SET/MOS

Fig. 12. Simulated waveform of 8-bit ADC Hybrid SET/MOS

| The simulation parameters      | Hybrid 4-bit<br>ADC [14]                                                                                                                         | Improved ADC                                                                                                                  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Power supply voltage           | 0.3V                                                                                                                                             | 0.1V                                                                                                                          |  |

| Power<br>dissipation           | 2.52E-10W                                                                                                                                        | 3.25E-11W                                                                                                                     |  |

| Capacitance<br>Array Block (F) | C=1E-12F                                                                                                                                         | C=10E-12F                                                                                                                     |  |

| Capacitive drive<br>capability | several fFs                                                                                                                                      | several hundreds<br>of fFs=500fF                                                                                              |  |

| Temperature (K)                | 100K                                                                                                                                             | 20-1000K                                                                                                                      |  |

| Total job time                 | 38.27Sec                                                                                                                                         | 15.86Sec                                                                                                                      |  |

| SET<br>parameters              | $\begin{array}{c} C_{G1} = 1.8E \text{-} 18F \\ C_{G2} = 0.64E \text{-} 18F \\ C_1 = C_2 = 1E \text{-} 19F \\ R_1 = R_2 = 2E6\Omega \end{array}$ | $\begin{array}{c} C_{G1}{=}2E{-}18F\\ C_{G2}{=}0.7E{-}18F\\ C_{1}{=}C_{2}{=}1E{-}19F\\ R_{1}{=}R_{2}{=}1E6\Omega \end{array}$ |  |

| NMOS<br>parameters             | M <sub>1</sub> : L= 150nm<br>W= 30nm<br>Depletion type                                                                                           | $\begin{array}{c} M_1: L{=}150nm\\ W{=}15nm\\ V_{to}{=}{-}0.018V\\ Depletion type \end{array}$                                |  |

Table 2. Comparison between the previously reportedADC in [14] and the improved ADC

# 4. Simulation results of 8-bit ADC circuit using SET

Single Electron Transistor inverter consists of two SETs in series, Fig. 13 shows the circuit diagram for a SET inverter. To simulate a SET inverter with 50% duty ratio,  $V_G$  has been adjusted to  $V_{G1}=0V$  and  $V_{G2}=-0.16V$ [22]. When the upper SET turns on, the lower SET turns off because SET has the inherent Coulomb oscillation characteristics with the period of  $q/C_g$  [22]. The circuit parameters are as follows: The supply voltage V<sub>DD</sub>=10mV, C<sub>G1</sub>=0.24E-18, C<sub>G2</sub>=0, the capacitances of junctions C<sub>1</sub>=C<sub>2</sub>=1.3E-18, tunnel the resistances of tunnel junctions  $R_1 = R_2 = 1.3E6$ , T=30K and the load capacitance  $C_L$ = 1pF[22].

Fig. 13. Schematic of SET inverter [5]

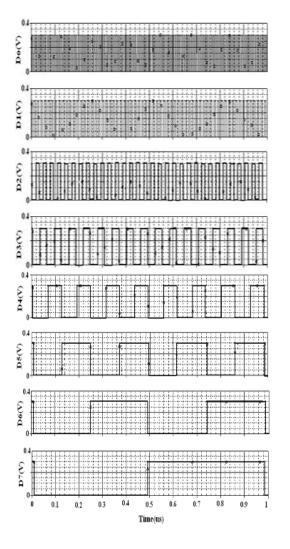

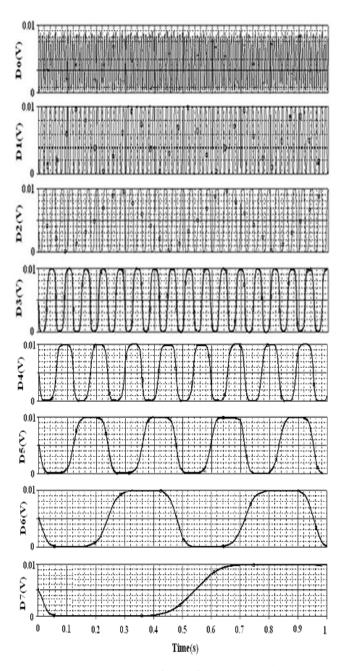

Using SET inverter as a unit circuit, as shown in Fig. 8, an 8-bit ADC architecture is simply implemented with a capacitive divider, and eight SET inverters with the same circuit parameters. In the 8-bit ADC circuit, the analog signal input is divided into  $V_{in}/2^{i}$  where i=0,1,2,3,4,5,6,7 by the capacitive divider, then it is encoded into the corresponding 8-bit digital signals  $D_0, D_1, D_2, D_3, D_4, D_5, D_6, D_7$ by the SET inverters. Fig. 14 shows the simulated conversion characteristics of the 8-bit ADC based on SET inverter using Orcad Capture PSPICE.

The comparison of ADC using CMOS, ADC using SET and ADC using hybrid SET/MOS for a 3-bit ADC is presented in Table 3. The switching speed of SET circuits determined by its RC time constant. The size, speed and power consumption of ADC using CMOS is from [21]. For a 3-bit ADC realized using CMOS one would require 63-MOS transistor components [21], but when the 3-bit ADC is realized using SET, it requires 6-SET transistor and 8-capacitors components and 3-bit ADC using hybrid SET/MOS requires 9-MOS, 3-SET and 8capacitor. Conversion speed of ADC using SET and ADC using hybrid SET/MOS are equal and faster than CMOS. The power consumption for ADC using hybrid SET/MOS is smaller than ADC using SET and ADC using CMOS.

Fig. 14. Simulated waveform of 8-bit ADC using SET

| Simulation parameters | ADC using<br>CMOS     | ADC<br>using<br>SET      | ADC using<br>Hybrid<br>SET/MOS |

|-----------------------|-----------------------|--------------------------|--------------------------------|

| Size                  | 63 MOS<br>Trans. [21] | 6-SET<br>8-<br>capacitor | 9-MOS<br>3-SET<br>8-capacitor  |

| Speed                 | 250 MHz-<br>1GHz[21]  | Approx.<br>1GHz          | Approx.<br>1GHz                |

| Power<br>Consumption  | In range of mW[21]    | 3.49E-<br>8W             | 2.92E-10W                      |

Table 3. Comparison between ADC using CMOS, ADC using SET and the improved ADC using hybrid SET/MOS

#### **5.** Conclusion

In this paper, improved hybrid SET/MOS ADC and DAC circuits were implemented and simulated. The improved hybrid n-bit DAC nano-circuits are simulated (for n=4 and 8) using Orcad Capture PSPICE. The performance of the SET/MOS hybrid n-bit ADC circuits were simulated (for n=3 and 8). Also ADC circuits using Single Electron Transistor were simulated (for n=8) using Orcad Capture PSPICE. In our results, the transient operation of hybrid SET/MOS circuit-based DAC is successfully demonstrated at 1000K and ADC at 144K. This performance can be compared with the pure SET circuits, the improved converter circuits have been enhanced in the drive capability and the power dissipation. Compared with the other SET/MOS hybrid circuit, the implemented converter circuits have compact circuit structure, higher integration density, high speed, high load drivability, low current and low power dissipation.

#### References

[1] Y. Taur, D. A. Buchanan, W. Chen, D. Frank. K. Ismail, S. Lo, G. Sai-Ha1asz, R. Viswanathan, H. Wann, S. Wind, and H. Wong.: 'CMOS Scaling into the Nanometer Regime', Proceeding of the IEEE, Vol. 85(No.4):pp.486-504, 1997.

- [2] K.K. Likharev: 'Single-electron devices and their applications', Proc. IEEE, 87, pp. 606–632, 1999.

- [3] T.H. Wang: 'Research trends of the integration single-electron transistor', Physics, 2000, Vol.29 (1): 58-59.

- [4] C. J. Gorter: 'A possible explanation of the increase of the electrical resistance of thin metal films at low temperatures and small field strengths', Physica, vol. 17, no. 8, pp. 777–780, Aug. 1951.

- [5] G. Lientshnig, I. Weymann, and P. Hadley: 'Simulating hybrid circuits of single-electron transistors and field effect transistors', Jpn. J. Appl. Phys., Vol. 42, Part 1, No.10, pp. 6467-6472, 2003.

- [6] S. J. Ahn and D. M. Kim: 'Asynchronous analogue-to-digital converter for single-electron circuits', Electron. Lett., vol. 34, pp. 172–173, 1998.

- [7] Y. Mizugaki and P. Delsing: 'Singleelectron signal modulator designed for a flash analog-to-digital converter', Jpn. J. Appl. Phys., vol. 40, pp. 6157– 6162, 2001.

- [8] C. H. Hu, J. F. Jiang, and Q. Y. Cai: 'A single-electron-transistor-based analog/digital converter', in Proc. IEEE-NANO, 2002, pp. 487–490.

- [9] C. Lageweg, S. Cotofana, and S. Vassiliadis: 'Digital to analog conversion performed in single electron technology', in Proc. IEEE-NANO, 2001, pp. 105–110.

- [10] J. Y. Le, J. F. Jiang, and Q. Y. Cai: 'Design of hybrid SET-CMOS D/A converter', Proc. IEEE, vol. 89, no. , pp. 299–302, 2001.

- [11] C. Hu, S. D. Cotofana, and J. Jiang: 'Analog-to-digital converter based on single-electron tunneling transistor', IEEE Trans. VLSI Syst., vol. 12, no.

11, pp. 1209–1213, Nov. 2004.

- [12] Q. Li, L. Cai, and S. Wang: 'A novel half adder circuit using hybrid single electron and MOS transistors', Journal of AFEU (Natural Science Edition), 2008, 9(1):78-81.

- [13] Q. Li, L. Cai, and Y.J. Zhou: 'Design and simulation of logic circuits by combined single-electron/MOS transistor structures', Proceedings of the 3th IEEE NEMS January 6-9, 2008, Sanya, China, pp.210-214.

- [14] Qin Li, Li Cai, and Gang Wu: 'Digital-Analog and Analog-Digital Converters Based on single-electron and MOS transistors', 2010, 8th IEEE International Conference on Control and Automation Xiamen, China, June 9-11, 2010.

- [15] C. Wasshuber: 'Computational singleelectronics [M]', New York: Springer-Verlag, 2001.

- [16] C. H. Hu, S. D. Cotofana and J.F. Jiang: 'Digital to Analogue converter based on single-electron tunneling transistor', IEE Proc.-Circuits Devices Syst., 2004, 10, Vol. 151(5): 438-442. 2004,10.

- [17] C. Lageweg, S. Cotofana, and S. Vassiliadis: 'Digital to analog conversion performed in single electron technology', in Proc. IEEE-NANO, 2001, pp. 105–110.

- [18] C. Hu, S. D. Cotofana, and J. Jiang: 'Analog-to-digital converter based on single-electron tunneling transistor', IEEE Trans. VLSI Syst., vol. 12, no. 11, pp. 1209–1213, Nov. 2004.

- [19] M-J Chun and Y-h Jeong: 'SET/CMOS universal literal gatebased Analog-to-Digital converter', the 3rd IEEE Conference on Nanotechnology, 12-14 Aug. 2003, Vol.2, pp.745-748.

- [20] S-W Jung, B-H Lee, and Y-H Jeong: 'Digital quantizer based on single electron box for multi-valued logic

circuits', Proceedings of 2005 5th IEEE Conference on Nanotechnology, Nagoya, Japan, July 2005: 156-159.

- [21] Clemens Maria Hammerschied: 'CMOS A/D converters using MOSFET only R-2R ladder Dissertation', Swiss federal institute of Technology, (2000).

- [22] Choong Hyun Lee, Se Woon Kim, Jang Uk Lee, Seung Hwan Seo, Gu-Cheol Kang, Kang Sup Roh, Kwan Young Kim, Soon Young Lee, Dong Myong Kim, Member, IEEE, and Dae Hwan Kim: 'Design of a Robust Analog-to-Digital Converter Based on Complementary SET/CMOS Hybrid Amplifier', IEEE Transactions on nanotechnology, Vol. 6, No. 6, November 2007.

- [23] Abeer I. Ammar, Sameh E. Rehan, Abdel-Fattah I. Abdel-Fattah: 'Design and simulation of single-source single-electron compleme-ntary 4-bit multiplexing nano-circuits', Communications and Electronics Engineering Department, Mansoura University, Egypt, Microelectronics Journal 43 (2012) 473–483.

- [24] Sameh E. Rehan: 'The implementation of 2-bit decoders using single electron linear threshold gates (LTGs)', in: Proceedings of the 22nd International Conference on Microelectronics (ICM 2010), Cairo, Egypt, December 19–22, 2010.

- [25] A. K. Abu El-Seoud, M. El-Banna and M. A. Hakim: 'On modelling and characterization of single electron transistor', International Journal of Electronics, Vol. 94, No. 6, June 2007, 573–585.